Address input : A[15:0]

active command 인 경우 Row(행)주소 read/write인 경우 Column(열) 주소

Precharge command A10이 Low일 때 특정 bank, high일 때 모든 bank를 선택

MRS(mode register set)또는 EMRS command 동안 op-code(operation)를 제공

Bank address inputs : BA[2:0]

Active, Read, Write, Pre-charge command 경우 bank 주소

256Mb, 512Mb에서는 BA2를 사용하지 않음(256Mb, 512Mb bank가 4개)

MRS(mode register set) 또는 EMRS command 동안 MRS mode를 지정

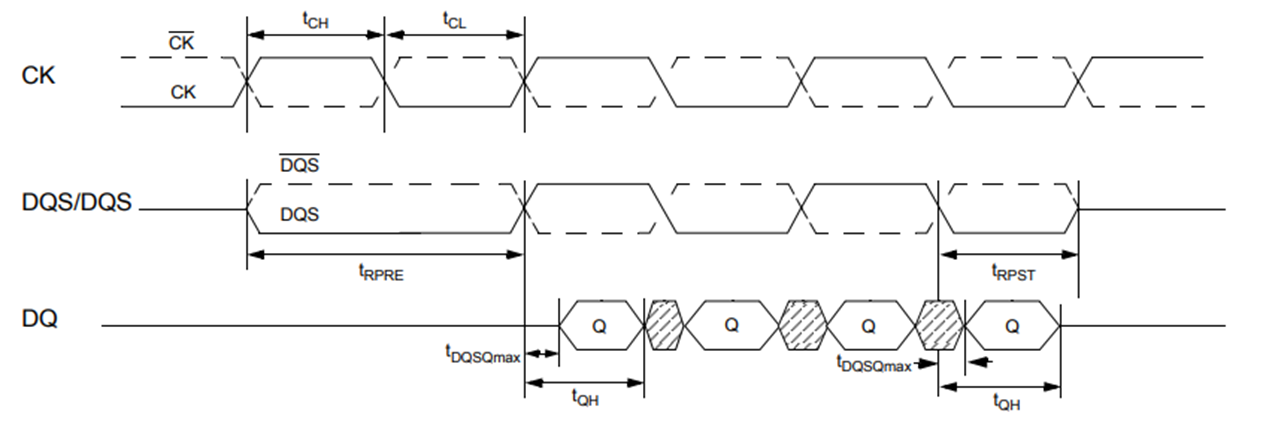

Clock : CK, CK

CK 및 CK은 differential clock

주소 및 제어 입력 신호는 CK의 positive edge와 CK의 negative edge 교차점에서 샘플링

출력 데이터(DQ 및 DQS/ DQS)는 CK 및 CK의 교차점을 참조

Clock enable : CKE

CKE가 HIGH가 되면 내부 clock과 버퍼, 외부 드라이버가 활성화되고 LOW가 되면 비활성화

Chip Select : CS

CS가 high 모든 명령이 masking

CS는 여러 rank가 있는 시스템에서 rank 선택 기능을 제공

Input Data Mask : DM(UDM, LDM)

DM은 Write data에 대한 input mask 신호

write중 DM이 high가 되면 input data는 masking

DQS 양쪽 edge에서 sampling

LDM은 하위 byte DQ[7:0]에 대한 DM이고 UDM은 상위 byte DQ[15:8]에 대한 DM

On-die termination : ODT

선로의 끝에 부딪히면 신호가 반사되게 되며 이는 noise가 되어 신호품질 하락

신호품질 하락을 방지하기 위해 DRAM 내부에 저항 추가

ODT가 HIGH가 되면 termination resistance를 활성화

x4, x8인 경우 DQ, DQS, DQS, RDQS, RDQS, DM 신호에 적용

x16인 경우 DQ, UDQS, UDQS, LDQS, LDQS, UDM, LDM 신호에 적용

EMR(1)에서 비활성화, 저항의 크기 설정 가능

Command input : RAS, CAS, WE

RAS(Row Address Strobe), CAS(Column Address Strobe)

DRAM은 메모리 셀이 행과 열을 가지는 array행태

address 신호는 행,열이 따로 되어 있지 않고 같은 신호 라인을 사용

메모리 주소를 지정 할 때 행(Row), 열(Column)을 구분하는 신호 필요

WE(Write Enable)

write mode, read mode 구분하기 위한 신호

high일 때 read, low일 때 write

DQ : Data Input/ Output

Data bus로 write일 때 input data, read일 때는 output data

DQS(UDQS, LDQS, RDQS), DQS(UDQS, LDQS, RDQS)

read, write 중 data(DQ)를 capture하는 데 사용

read에서는 DQ의 edge에서 정렬되고 write에서는 중앙에 위치

EMR(1)[A10]의 제어 비트를 이용하여 differential pair signal(DQS) 사용 가능