CKE Low Anytime

DDR2 SDRAM applications may go into a reset state anytime during normal operation.

DDR2 SDRAM 응용 프로그램은 정상 작동 중 언제든지 Reset 상태로 전환될 수 있습니다.

If an application enters a reset condition, CKE is used to ensure the DDR2 SDRAM device resumes normal operation after reinitializing.

어플리케이션이 Reset 상태에 진입하면, CKE가 사용되어 DDR2 SDRAM 장치가 재초기화 후 정상 작동을 재개하도록 보장합니다.

All data will be lost during a reset condition;

Reset 상태 동안 모든 데이터가 손실될 것입니다;

however, the DDR2 SDRAM device will continue to operate properly if the following conditions outlined in this section are satisfied.

그러나, 이 부분에 기술된 다음 조건들이 충족된다면, DDR2 SDRAM 장치는 제대로 계속 작동할 것입니다.

The reset condition defined here assumes all supply voltages (VDD, VDDQ, VDDL, and VREF) are stable and meet all DC specifications prior to, during, and after the RESET operation.

여기에서 정의된 Reset 조건은 모든 공급 전압 (VDD, VDDQ, VDDL, 그리고 VREF)이 안정적이며, Reset 작업 이전, 동안, 그리고 이후에 모든 DC 사양을 만족시킨다는 것을 가정합니다.

All other input balls of the DDR2 SDRAM device are a "Don't Care" during RESET with the exception of CKE.

DDR2 SDRAM 장치의 모든 다른 입력 볼(입력 단자)들은 Reset 동안 'Don't Care'는 상태가 되며, 이는 CKE를 제외합니다.

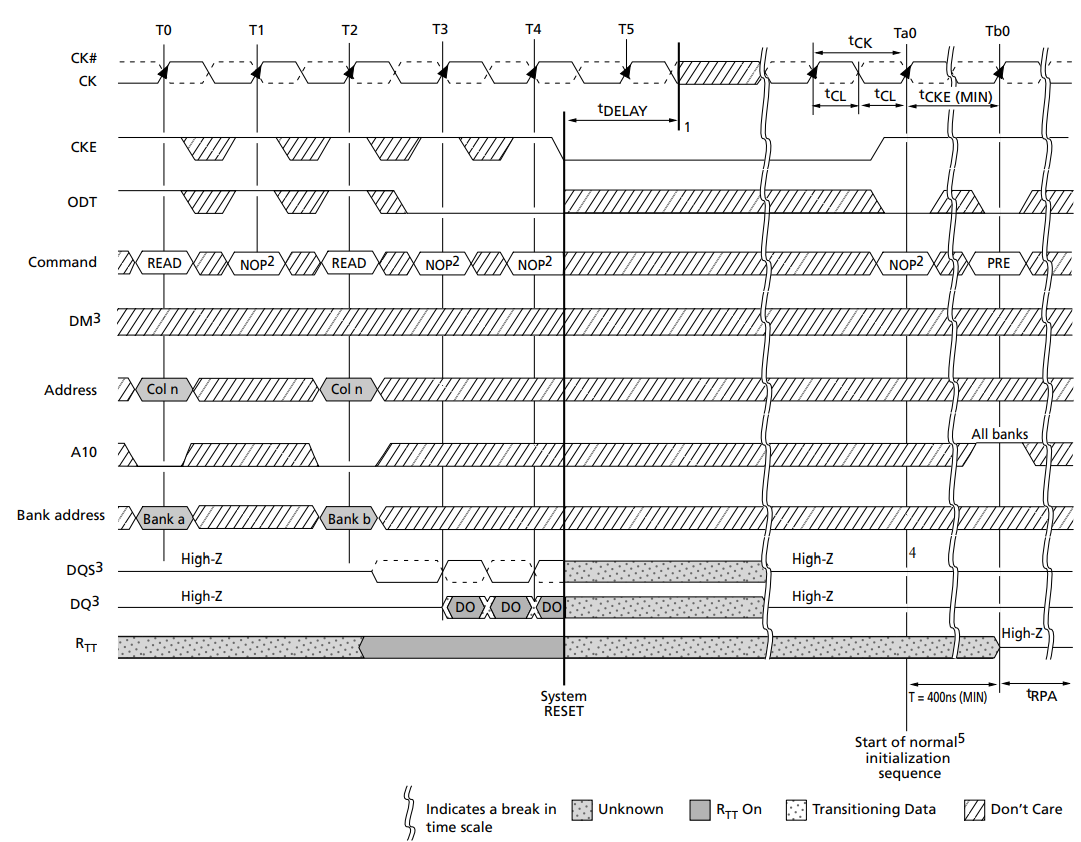

If CKE asynchronously drops LOW during any valid operation (including a READ or WRITE burst), the memory controller must satisfy the timing parameter tDELAY before turning off the clocks.

만약 CKE가 어떤 유효한 작업(READ나 WRITE 버스트를 포함하여) 도중에 비동기적으로 LOW 상태로 떨어진다면, 메모리 컨트롤러는 클록을 끄기 전에 타이밍 파라미터 tDELAY를 만족시켜야 합니다.

Stable clocks must exist at the CK, CK# inputs of the DRAM before CKE is raised HIGH, at which time the normal initialization sequence must occur (see initialization).

DRAM의 CK, CK# 입력에서 안정된 클럭이 존재해야 하며, 이는 CKE가 HIGH 상태로 올라가기 전이어야 합니다. 그 때에는 정상 initialization 시퀀스가 발생해야 합니다(initialization를 참조).

The DDR2 SDRAM device is now ready for normal operation after the initialization sequence.

initialization 시퀀스 이후, DDR2 SDRAM 장치는 이제 정상 작동을 위해 준비가 되었습니다.

Figure 80 shows the proper sequence for a RESET operation.

Figure 80은 RESET 작업에 대한 적절한 순서를 보여줍니다.

1. VDD, VDDL, VDDQ, VTT, and VREF must be valid at all times.

1. VDD, VDDL, VDDQ, VTT, 그리고 VREF는 항상 유효해야 합니다.

2. Either NOP or DESELECT command may be applied.

2. NOP 또는 DESELECT Command이 적용될 수 있습니다.

3. DM represents DM for x4/x8 configuration and UDM, LDM for x16 configuration. DQS represents DQS, DQS#, UDQS, UDQS#, LDQS, LDQS#, RDQS, and RDQS# for the appropriate configuration (x4, x8, x16.

3. DM은 x4/x8 구성에 대한 DM을, 그리고 UDM, LDM은 x16 구성을 나타냅니다. DQS는 적절한 구성(x4, x8, x16)에 대한 DQS, DQS#, UDQS, UDQS#, LDQS, LDQS#, RDQS, RDQS#을 나타냅니다.

4. In certain cases where a READ cycle is interrupted, CKE going HIGH may result in the completion of the burst.

4. READ 사이클이 중단되는 특정한 경우에서, CKE가 HIGH 상태로 가는 것은 버스트가 완료될 수 있다."

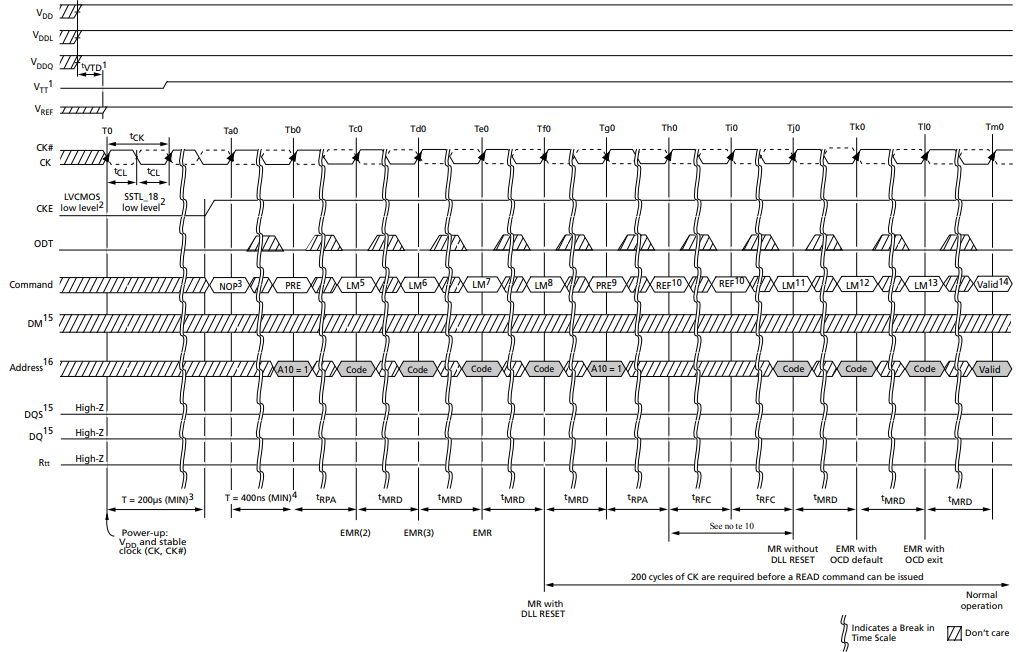

5. Initialization timing is shown in Figure 43.

5. Initialization timing 그림 43에서 보여집니다.