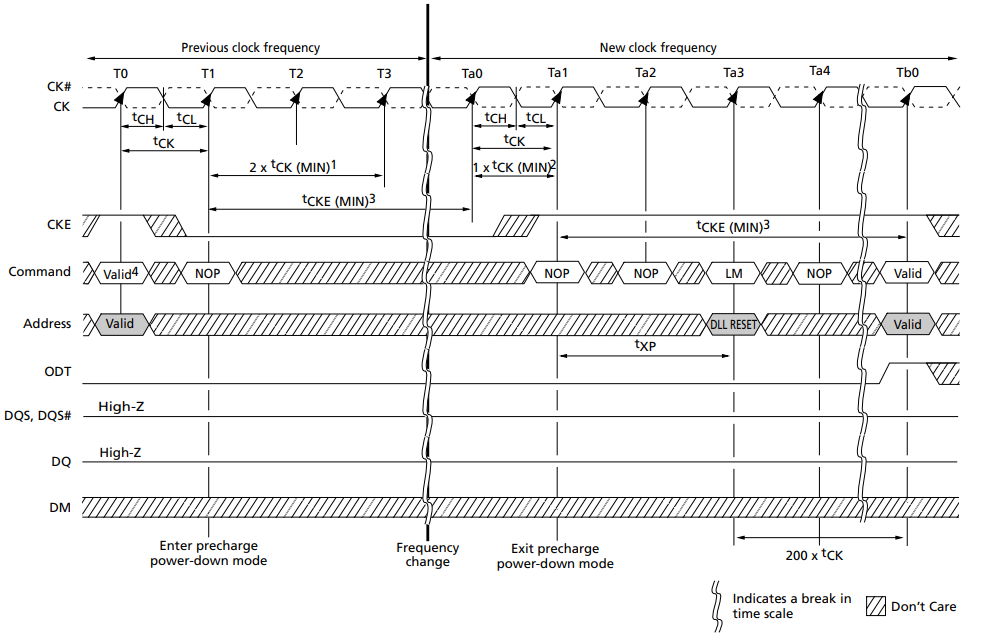

When the DDR2 SDRAM is in precharge power-down mode, ODT must be turned off and CKE must be at a logic LOW level.

DDR2 SDRAM이 precharge power-down mode일 때 OPT는 꺼져 있어야 한다. 그리고 CKE는 LOW 이어야 한다.

A minimum of two differential clock cycles must pass after CKE goes LOW before clock frequency may change.

클럭 주파수가 변경되기 전, 최소 두 개의 differential clock cycles이 CKE이 LOW가 된 후에 지나가야 한다.

The device input clock frequency is allowed to change only within minimum and maximum operating frequencies specified for the particular speed grade.

입력 클럭 주파수는 속도 단계가 지정된 minimum and maximum operating frequencies내에서만 변경할 수 있다.

During input clock frequency change, ODT and CKE must be held at stable LOW levels.

입력 clock 주파수 동안, ODT and CKE은 안전된 LOW에서 유지되어야 한다.

When the input clock frequency is changed, new stable clocks must be provided to the device before precharge powerdown may be exited, and DLL must be reset via MR after precharge power-down exit.

precharge powerdown이 종료되기 전에 클럭 주파수가 변경되면 새로운 안정된 clock이 장치에 제공되어야 한다. 그리고 precharge powerdown이 종료 후에 DLL은 MR을 통해 RESET되어야 한다.

Depending on the new clock frequency, additional LM commands might be required to adjust the CL, WR, AL, and so forth.

새로운 clock 주파수에 따라, 추가적인 LM 명령어들이 CL, WR, AL 등등을 조정하기 위해 필요하다.

Depending on the new clock frequency, an additional LM command might be required to appropriately set the WR MR9, MR10, MR11.

새로운 clock 주파수에 따라, 추가적인 LM 명령어들이 WR MR9, MR10, MR11을 설정하기 위해 필요하다.

During the DLL relock period of 200 cycles, ODT must remain off.

200 사이클의 DLL relock 기간 동안 ODT는 꺼져 있어야 한다.

After the DLL lock time, the DRAM is ready to operate with a new clock frequency.

DLL lock 시간 이후에, DRAM은 새로운 clock 주파수로 작동 준비가 되어 있다.

1. A minimum of 2 × tCK is required after entering precharge power-down prior to changing clock frequencies.

1. 클럭 주파수가 변경하기 전, precharge power-down에 들어간 후 최소 2 x tCK가 필요하다.

2. When the new clock frequency has changed and is stable, a minimum of 1 × tCK is required prior to exiting precharge power-down.

2. 새로운 클럭 주파수가 변경되고 안정화되면, precharge power-down에 나가기 전 최소 1 x tCK가 필요하다.

3. Minimum CKE high time is tCKE = 3 × tCK. Minimum CKE LOW time is tCKE = 3 × tCK. This requires a minimum of three clock cycles of registration.

3. 최소 CLE HIGH 시간은 tCKE = 3 x tCK. 최소 CLE LOW 시간은 tCKE = 3 x tCK. 최소한 3개의 클럭 사이클이 필요하다.

4. If this command is a PRECHARGE (or if the device is already in the idle state), then the power-down mode shown is precharge power-down, which is required prior to the clock frequency change.

4. Command가 PRECHARGE(또는 IDLE)이면 power-down mode는 precharge power-down mode이며, 클럭 주파수 변경전에 필요하다.

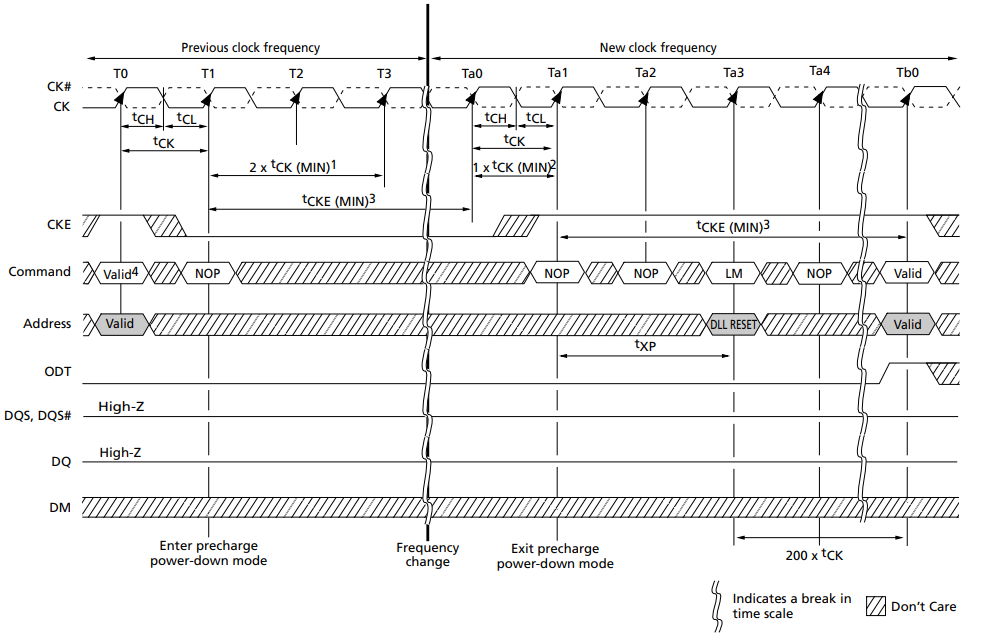

When the DDR2 SDRAM is in precharge power-down mode, ODT must be turned off and CKE must be at a logic LOW level.

DDR2 SDRAM이 precharge power-down mode일 때 OPT는 꺼져 있어야 한다. 그리고 CKE는 LOW 이어야 한다.

A minimum of two differential clock cycles must pass after CKE goes LOW before clock frequency may change.

클럭 주파수가 변경되기 전, 최소 두 개의 differential clock cycles이 CKE이 LOW가 된 후에 지나가야 한다.

The device input clock frequency is allowed to change only within minimum and maximum operating frequencies specified for the particular speed grade.

입력 클럭 주파수는 속도 단계가 지정된 minimum and maximum operating frequencies내에서만 변경할 수 있다.

During input clock frequency change, ODT and CKE must be held at stable LOW levels.

입력 clock 주파수 동안, ODT and CKE은 안전된 LOW에서 유지되어야 한다.

When the input clock frequency is changed, new stable clocks must be provided to the device before precharge powerdown may be exited, and DLL must be reset via MR after precharge power-down exit.

precharge powerdown이 종료되기 전에 클럭 주파수가 변경되면 새로운 안정된 clock이 장치에 제공되어야 한다. 그리고 precharge powerdown이 종료 후에 DLL은 MR을 통해 RESET되어야 한다.

Depending on the new clock frequency, additional LM commands might be required to adjust the CL, WR, AL, and so forth.

새로운 clock 주파수에 따라, 추가적인 LM 명령어들이 CL, WR, AL 등등을 조정하기 위해 필요하다.

Depending on the new clock frequency, an additional LM command might be required to appropriately set the WR MR9, MR10, MR11.

새로운 clock 주파수에 따라, 추가적인 LM 명령어들이 WR MR9, MR10, MR11을 설정하기 위해 필요하다.

During the DLL relock period of 200 cycles, ODT must remain off.

200 사이클의 DLL relock 기간 동안 ODT는 꺼져 있어야 한다.

After the DLL lock time, the DRAM is ready to operate with a new clock frequency.

DLL lock 시간 이후에, DRAM은 새로운 clock 주파수로 작동 준비가 되어 있다.

1. A minimum of 2 × tCK is required after entering precharge power-down prior to changing clock frequencies.

1. 클럭 주파수가 변경하기 전, precharge power-down에 들어간 후 최소 2 x tCK가 필요하다.

2. When the new clock frequency has changed and is stable, a minimum of 1 × tCK is required prior to exiting precharge power-down.

2. 새로운 클럭 주파수가 변경되고 안정화되면, precharge power-down에 나가기 전 최소 1 x tCK가 필요하다.

3. Minimum CKE high time is tCKE = 3 × tCK. Minimum CKE LOW time is tCKE = 3 × tCK. This requires a minimum of three clock cycles of registration.

3. 최소 CLE HIGH 시간은 tCKE = 3 x tCK. 최소 CLE LOW 시간은 tCKE = 3 x tCK. 최소한 3개의 클럭 사이클이 필요하다.

4. If this command is a PRECHARGE (or if the device is already in the idle state), then the power-down mode shown is precharge power-down, which is required prior to the clock frequency change.

4. Command가 PRECHARGE(또는 IDLE)이면 power-down mode는 precharge power-down mode이며, 클럭 주파수 변경전에 필요하다.