3.1 Control Interface

DFI 스펙은 DRAM 장치로 메모리 address, command, control 신호를 전달하는 데 필요한 신호를 정의하며, 이 신호들은 DFI와 DRAM 사이의 실제 지연 시간(tctrl_delay)을 고려하여 타이밍을 유지하면서 DRAM으로 전달됩니다.

DFI 스펙은 메모리 기술에 따라 필요한 특정 Control 신호를 포함하며, 예를 들어 dfi_reset_n 신호는 DDR3, dfi_odt 신호는 DDR2와 DDR3, 그리고 dfi_rddata_dnv 신호는 LPDDR2 메모리 시스템에 특화되어 있습니다.

frequency ratio systems에서는 DFI PHY 클럭의 각 phase(N)에 대한 신호 값을 정의하는 '_pN' 접미사가 붙은 phase별 신호로 control 인터페이스의 신호가 복제되며, 메모리 컨트롤러(MC)는 PHY와 통신하기 위해 어느 단계에서든 명령을 내릴 수 있습니다.

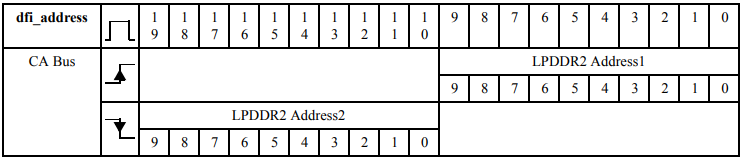

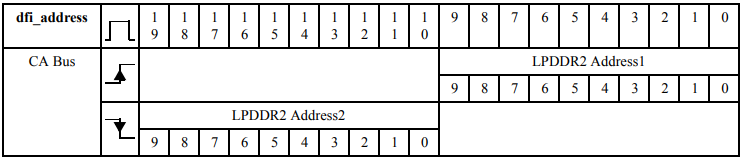

LPDDR2 메모리 시스템에서는 CA 버스가 dfi_address 버스에 매핑되며, 이때 dfi_address 버스는 최소 20비트를 가져야 하고, PHY는 상승 및 하강 CA 단계를 선택하여 LPDDR2 메모리에 10비트의 더블 데이터 속도 출력을 보낼 책임이 있습니다.

Control Signals

| Signal | From | Width | Default | Description |

| dfi_address or dfi_address_pN |

MC | DFI address Width | .a | DRAM에 전달되는 address 정보를 정의 dfi_address 신호의 비트 순서를 그대로 유지 frequency ratio system에서 address 신호가 각 PHY의 단계(N)에 대한 address를 정의(dfi_address_pN) LPDDR2에서 dfi_address는 특정 CA버스와 연결 |

| dfi_bank or dfi_bank_pN |

MC | DFI Bank Width | .b | DRAM에 전달되는 bank 정보를 정의 dfi_bank 신호의 비트 순서를 그대로 유지 frequency ratio system에서 bank 신호가 각 PHY의 단계(N)에 대한 bank를 정의(dfi_bank_pN) DDR1, LPDDR1, DDR2, DDR3에서만 적용되며, LPDDR2에서는 IDLE 상태로 유지 |

| dfi_cas_n or dfi_cas_n_pN |

MC | DFI Control Width | 0x1 | DRAM에 전달되는 Column Address Stribe(CAS) 정보를 정의 frequency ratio system에서 CAS 신호가 각 PHY의 단계(N)에 대한 Column를 정의(dfi_cas_n_pN) DDR1, LPDDR1, DDR2, DDR3에서만 적용되며, LPDDR2에서는 IDLE 상태로 유지 |

| dfi_cke or dfi_cke_pN |

MC | DFI Chip Select Width | 0x0 0x1 |

Clock Enable(CKE) 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 clock enable 관리 MC는 모든 clock phase에서 정보를 제어하고, PHY는 어떤 phase에서든 명령을 수락 |

| dfi_cs_n or dfi_cs_n_pN |

MC | DFI Chip Select Width | 0x1 | Chip select 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 CS 정보 관리 |

| dfi_odt or dfi_odt_pN |

MC | DFI Chip Select Width | 0x0 | On-Die Termination(ODT) 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 ODT 정보 관리 MC는 모든 clock phase에서 정보를 제어하고, PHY는 어떤 phase에서든 명령을 수락 DDR2와 DDR3 메모리 시스템에서만 필요 |

| dfi_ras or dfi_ras_n_pN |

MC | DFI Control Width | 0x1 | Row Address Strobe 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 RAS 정보 관리 DDR1, LPDDR1, DDR2, DDR3 시스템에만 적용 LPDDR2에서는 IDLE 상태로 유지 |

| dfi_reset_n or dfi_reset_n_pN |

MC | DFI Chip Select Width | 0x0 | RESET 정보를 정의 DDR3 시스템에서만 필요 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 RESET 정보 관리 |

| dfi_we_n or dfi_we_n_pN |

MC | DFI Control Width | 0x1 | Write Enable(WE_n) 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 WE_n 정보 관리 DDR1, LPDDR1, DDR2, DDR3에서만 이 기능이 적용되며, LPDDR2에서는 IDLE 상태로 유지 |

a. 이 신호는 initialization 중에는 의미가 없습니다. 따라서 이 신호에 대해 기본값을 유지할 필요가 없습니다. LPDDR2 메모리 시스템의 경우 dfi_init_complete가 활성화될 때까지 dfi_address 신호는 NOP로 구동되어야 합니다.

b. 이 신호는 initialization 중에는 의미가 없습니다. 따라서 이 신호에 대해 기본값을 유지할 필요가 없습니다.

c. 대부분의 메모리 장치는 리셋 시 CKE를 LOW 정의합니다. 그러나 모바일 DDR과 같은 일부 장치는 리셋 시 CKE를 HIGH 정의합니다. 기본값은 메모리 정의를 반영해야 합니다.

Control Timing Parameter

| Parameter | Defined by | Min | Max | Unit | Description |

| tctrl_delay | PHY | 0 | .a | DFI clock cycles |

DFI 제어 신호가 활성화 되거나 비활성화 된 후에 PHY-DRAM 인터페이스에서 제어 신호가 언제 반영되는지를 DFI 클럭 주기로 지정 DFI 클럭과 메모리 클럭이 정확히 일치하지 않는다면, 이 값은 다음 정수로 반올림 |

a. DFI는 최대값을 지정하지 않습니다. 지원되는 값의 범위는 구현에 따라 다릅니다.

3.1 Control Interface

DFI 스펙은 DRAM 장치로 메모리 address, command, control 신호를 전달하는 데 필요한 신호를 정의하며, 이 신호들은 DFI와 DRAM 사이의 실제 지연 시간(tctrl_delay)을 고려하여 타이밍을 유지하면서 DRAM으로 전달됩니다.

DFI 스펙은 메모리 기술에 따라 필요한 특정 Control 신호를 포함하며, 예를 들어 dfi_reset_n 신호는 DDR3, dfi_odt 신호는 DDR2와 DDR3, 그리고 dfi_rddata_dnv 신호는 LPDDR2 메모리 시스템에 특화되어 있습니다.

frequency ratio systems에서는 DFI PHY 클럭의 각 phase(N)에 대한 신호 값을 정의하는 '_pN' 접미사가 붙은 phase별 신호로 control 인터페이스의 신호가 복제되며, 메모리 컨트롤러(MC)는 PHY와 통신하기 위해 어느 단계에서든 명령을 내릴 수 있습니다.

LPDDR2 메모리 시스템에서는 CA 버스가 dfi_address 버스에 매핑되며, 이때 dfi_address 버스는 최소 20비트를 가져야 하고, PHY는 상승 및 하강 CA 단계를 선택하여 LPDDR2 메모리에 10비트의 더블 데이터 속도 출력을 보낼 책임이 있습니다.

Control Signals

| Signal | From | Width | Default | Description |

| dfi_address or dfi_address_pN |

MC | DFI address Width | .a | DRAM에 전달되는 address 정보를 정의 dfi_address 신호의 비트 순서를 그대로 유지 frequency ratio system에서 address 신호가 각 PHY의 단계(N)에 대한 address를 정의(dfi_address_pN) LPDDR2에서 dfi_address는 특정 CA버스와 연결 |

| dfi_bank or dfi_bank_pN |

MC | DFI Bank Width | .b | DRAM에 전달되는 bank 정보를 정의 dfi_bank 신호의 비트 순서를 그대로 유지 frequency ratio system에서 bank 신호가 각 PHY의 단계(N)에 대한 bank를 정의(dfi_bank_pN) DDR1, LPDDR1, DDR2, DDR3에서만 적용되며, LPDDR2에서는 IDLE 상태로 유지 |

| dfi_cas_n or dfi_cas_n_pN |

MC | DFI Control Width | 0x1 | DRAM에 전달되는 Column Address Stribe(CAS) 정보를 정의 frequency ratio system에서 CAS 신호가 각 PHY의 단계(N)에 대한 Column를 정의(dfi_cas_n_pN) DDR1, LPDDR1, DDR2, DDR3에서만 적용되며, LPDDR2에서는 IDLE 상태로 유지 |

| dfi_cke or dfi_cke_pN |

MC | DFI Chip Select Width | 0x0 0x1 |

Clock Enable(CKE) 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 clock enable 관리 MC는 모든 clock phase에서 정보를 제어하고, PHY는 어떤 phase에서든 명령을 수락 |

| dfi_cs_n or dfi_cs_n_pN |

MC | DFI Chip Select Width | 0x1 | Chip select 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 CS 정보 관리 |

| dfi_odt or dfi_odt_pN |

MC | DFI Chip Select Width | 0x0 | On-Die Termination(ODT) 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 ODT 정보 관리 MC는 모든 clock phase에서 정보를 제어하고, PHY는 어떤 phase에서든 명령을 수락 DDR2와 DDR3 메모리 시스템에서만 필요 |

| dfi_ras or dfi_ras_n_pN |

MC | DFI Control Width | 0x1 | Row Address Strobe 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 RAS 정보 관리 DDR1, LPDDR1, DDR2, DDR3 시스템에만 적용 LPDDR2에서는 IDLE 상태로 유지 |

| dfi_reset_n or dfi_reset_n_pN |

MC | DFI Chip Select Width | 0x0 | RESET 정보를 정의 DDR3 시스템에서만 필요 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 RESET 정보 관리 |

| dfi_we_n or dfi_we_n_pN |

MC | DFI Control Width | 0x1 | Write Enable(WE_n) 정보를 정의 frequency ratio system : 여러 phase의 clock이 있는 시스템에서는 각 phase마다 별도의 WE_n 정보 관리 DDR1, LPDDR1, DDR2, DDR3에서만 이 기능이 적용되며, LPDDR2에서는 IDLE 상태로 유지 |

a. 이 신호는 initialization 중에는 의미가 없습니다. 따라서 이 신호에 대해 기본값을 유지할 필요가 없습니다. LPDDR2 메모리 시스템의 경우 dfi_init_complete가 활성화될 때까지 dfi_address 신호는 NOP로 구동되어야 합니다.

b. 이 신호는 initialization 중에는 의미가 없습니다. 따라서 이 신호에 대해 기본값을 유지할 필요가 없습니다.

c. 대부분의 메모리 장치는 리셋 시 CKE를 LOW 정의합니다. 그러나 모바일 DDR과 같은 일부 장치는 리셋 시 CKE를 HIGH 정의합니다. 기본값은 메모리 정의를 반영해야 합니다.

Control Timing Parameter

| Parameter | Defined by | Min | Max | Unit | Description |

| tctrl_delay | PHY | 0 | .a | DFI clock cycles |

DFI 제어 신호가 활성화 되거나 비활성화 된 후에 PHY-DRAM 인터페이스에서 제어 신호가 언제 반영되는지를 DFI 클럭 주기로 지정 DFI 클럭과 메모리 클럭이 정확히 일치하지 않는다면, 이 값은 다음 정수로 반올림 |

a. DFI는 최대값을 지정하지 않습니다. 지원되는 값의 범위는 구현에 따라 다릅니다.