반응형

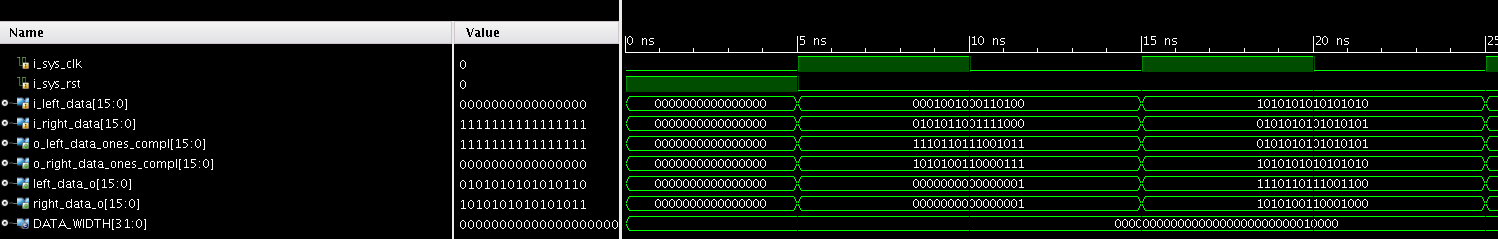

1's Complement

module Complement #(

parameter DATA_WIDTH=16

) (

input i_sys_clk,

input i_sys_rst,

input [DATA_WIDTH-1:0] i_left_data,

input [DATA_WIDTH-1:0] i_right_data,

output reg [DATA_WIDTH-1:0] o_left_data_ones_compl,

output reg [DATA_WIDTH-1:0] o_right_data_ones_compl

);

// 1's Complement

always @ (posedge i_sys_clk or posedge i_sys_rst)

if(i_sys_rst)

o_left_data_ones_compl <= DATA_WIDTH[1'b0];

else

o_left_data_ones_compl <= ~(i_left_data);

// 1's Complement

always @ (posedge i_sys_clk or posedge i_sys_rst)

if(i_sys_rst)

o_right_data_ones_compl <= DATA_WIDTH[1'b0];

else

o_right_data_ones_compl <= ~(i_right_data);

endmoduletb

`timescale 1ns/1ps

module Complement_TB();

reg [15:0] i_left_data;

reg [15:0] i_right_data;

wire [15:0] o_left_data_ones_compl;

wire [15:0] o_right_data_ones_compl;

reg i_sys_clk;

reg i_sys_rst;

// Instantiate the Complement module

Complement #(

.DATA_WIDTH(16)

) my_complement (

.i_sys_clk(i_sys_clk),

.i_sys_rst(i_sys_rst),

.i_left_data(i_left_data),

.i_right_data(i_right_data),

.o_left_data_ones_compl(o_left_data_ones_compl),

.o_right_data_ones_compl(o_right_data_ones_compl)

);

// Clock generation

always begin

#5 i_sys_clk = ~i_sys_clk;

end

// Testbench stimulus

initial begin

i_sys_clk = 0;

i_sys_rst = 1;

// Reset the module

#10 i_sys_rst = 0;

// Apply test inputs

i_left_data = 16'h1234;

i_right_data = 16'h5678;

#10;

i_left_data = 16'hAAAA;

i_right_data = 16'h5555;

#10;

i_left_data = 16'h0000;

i_right_data = 16'hFFFF;

#10;

// Finish the simulation

$finish;

end

endmodulesim

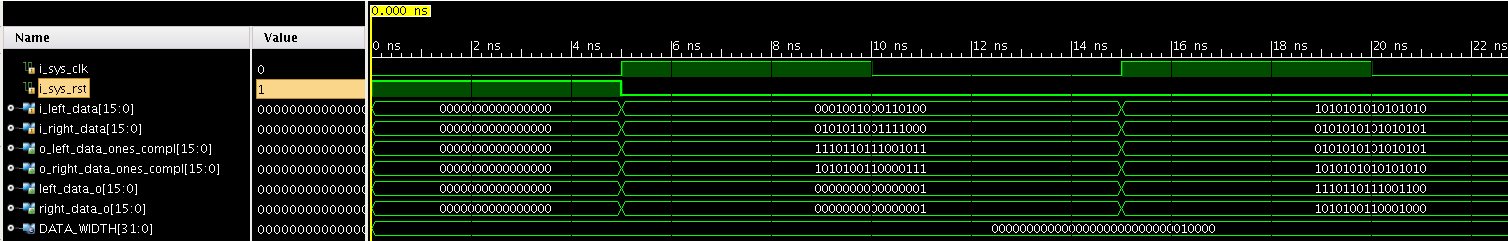

2's Complement

module Complement #(

parameter DATA_WIDTH=16

) (

input i_sys_clk,

input i_sys_rst,

input [DATA_WIDTH-1:0] i_left_data,

input [DATA_WIDTH-1:0] i_right_data,

output reg [DATA_WIDTH-1:0] o_left_data_ones_compl,

output reg [DATA_WIDTH-1:0] o_right_data_ones_compl,

output reg [DATA_WIDTH-1:0] left_data_o,

output reg [DATA_WIDTH-1:0] right_data_o

);

// 1's Complement

always @ (posedge i_sys_clk or posedge i_sys_rst)

if(i_sys_rst)

o_left_data_ones_compl <= DATA_WIDTH[1'b0];

else

o_left_data_ones_compl <= ~(i_left_data);

// 1's Complement

always @ (posedge i_sys_clk or posedge i_sys_rst)

if(i_sys_rst)

o_right_data_ones_compl <= DATA_WIDTH[1'b0];

else

o_right_data_ones_compl <= ~(i_right_data);

//Register the incoming parallel data of the left channel after

//conversion to 2's complement form

always @ (posedge i_sys_clk or posedge i_sys_rst)

if(i_sys_rst)

left_data_o <= DATA_WIDTH[1'b0];

else

left_data_o <= o_left_data_ones_compl + 1;

//Register the incoming parallel data of the right channel after

//conversion to 2's complement form

always @ (posedge i_sys_clk or posedge i_sys_rst)

if(i_sys_rst)

right_data_o <= DATA_WIDTH[1'b0];

else

right_data_o <= o_right_data_ones_compl + 1;

endmoduletb

`timescale 1ns/1ps

module Complement_TB();

reg [15:0] i_left_data;

reg [15:0] i_right_data;

wire [15:0] o_left_data_ones_compl;

wire [15:0] o_right_data_ones_compl;

wire [15:0] right_data_o;

wire [15:0] left_data_o;

reg i_sys_clk;

reg i_sys_rst;

// Instantiate the Complement module

Complement #(

.DATA_WIDTH(16)

) my_complement (

.i_sys_clk(i_sys_clk),

.i_sys_rst(i_sys_rst),

.i_left_data(i_left_data),

.i_right_data(i_right_data),

.o_left_data_ones_compl(o_left_data_ones_compl),

.o_right_data_ones_compl(o_right_data_ones_compl),

.left_data_o(left_data_o),

.right_data_o(right_data_o)

);

// Clock generation

always begin

#5 i_sys_clk = ~i_sys_clk;

end

// Testbench stimulus

initial begin

i_sys_clk = 0;

i_sys_rst = 1;

i_left_data = 16'h0000;

i_right_data = 16'h0000;

// Reset the module

#5 i_sys_rst = 0;

// Apply test inputs

i_left_data = 16'h1234;

i_right_data = 16'h5678;

#10;

i_left_data = 16'hAAAA;

i_right_data = 16'h5555;

#10;

i_left_data = 16'h0000;

i_right_data = 16'hFFFF;

#10;

// Finish the simulation

$finish;

end

endmodulesim

※ 추가적으로 공부할 내용

wire의 값은 바로 할당되는데

always @ (posedge i_sys_clk or posedge i_sys_rst)

if(i_sys_rst)

o_left_data_ones_compl <= DATA_WIDTH[1'b0];

else

o_left_data_ones_compl <= ~(i_left_data);reg는 바로 할당한되는 이유

always @ (posedge i_sys_clk or posedge i_sys_rst)

if(i_sys_rst)

left_data_o <= DATA_WIDTH[1'b0];

else

left_data_o <= o_left_data_ones_compl + 1;

반응형