특정 bank의 행을 open하는데 사용

Bank Address 값에 따라 Bank가 결정되고 Address값에 따라 행이 선택

open한 행은 bank에 Precharge command가 실행되기 될 때 까지 open으로 유지

같은 bank에서 다른 행을 열기 전에 Precharge command를 실행

Activate

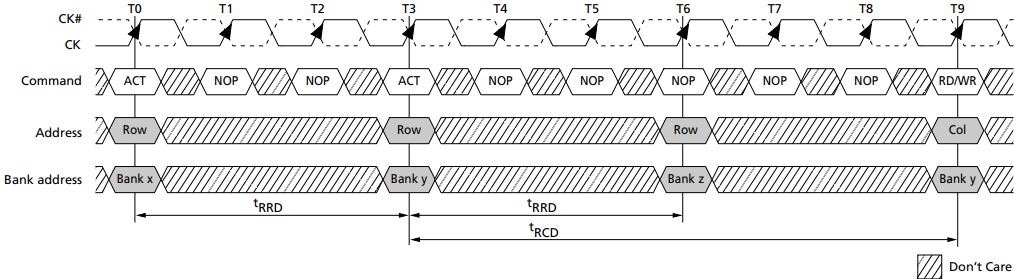

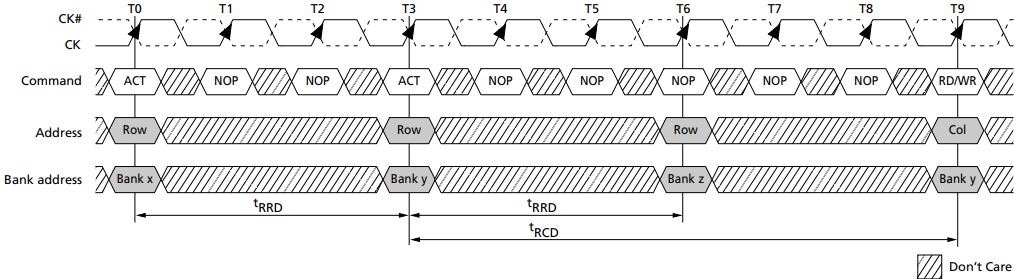

Meeting tRRD (MIN) and tRCD (MIN)

Before any READ or WRITE commands can be issued to a bank within the DDR2 SDRAM, a row in that bank must be opened (activated), even when additive latency is used.

DDR2 SDRAM 내의 bank에 어떤 읽기(READ) 혹은 쓰기(WRITE) 명령을 내리기 전에는, 해당 bank의 행(row)이 열려있어야 합니다. 이는 additive latency(AL)가 사용되는 경우에도 마찬가지입니다.

This is accomplished via the ACTIVATE command, which selects both the bank and the row to be activated.

이것은 ACTIVATE 명령을 통해 이루어지며, 이 명령은 활성화될 bank와 행(row)을 모두 선택합니다.

After a row is opened with an ACTIVATE command, a READ or WRITE command may be issued to that row subject to the tRCD specification.

ACTIVATE 명령을 사용해 행(row)이 열린 후에는, 해당 행에 READ 또는 WRITE 명령을 내릴 수 있습니다. 이는 tRCD 사양에 따라 가능합니다.

tRCD (MIN) should be divided by the clock period and rounded up to the next whole number to determine the earliest clock edge after the ACTIVATE command on which a READ or WRITE command can be entered.

tRCD (MIN)은 클럭 주기로 나눈 후, 그 결과를 다음 정수로 올려야 합니다. 이는 ACTIVATE 명령 후에 가장 빠른 클럭 엣지를 결정하기 위함이며, 이 클럭 엣지에서 READ 또는 WRITE 명령이 입력될 수 있습니다.

The same procedure is used to convert other specification limits from time units to clock cycles.

시간 단위의 다른 사양 제한을 클럭 주기로 변환하기 위해 같은 절차가 사용됩니다.

For example, a tRCD (MIN) specification of 20ns with a 266 MHz clock (tCK = 3.75ns) results in 5.3 clocks, rounded up to 6.

예를 들어, 266 MHz 클럭 (tCK = 3.75ns)을 가지고 20ns의 tRCD (MIN) 사양이 있다면, 이는 5.3 clock으로 결과가 나오며, 이는 6으로 올림됩니다.

This is shown in Figure 44, which covers any case where 5 < tRCD (MIN)/tCK ≤ 6.

Figure 44에서 이 내용이 보여지며, 이 그림은 5 < tRCD (MIN)/tCK ≤ 6인 모든 경우를 포괄하고 있습니다.

Figure 44 also shows the case for tRRD where 2 < tRRD (MIN)/tCK ≤ 3."

Figure 44는 또한 tRRD (MIN)/tCK이 2보다 크고 3보다 작거나 같은 경우의 tRRD 사례를 보여줍니다.

Multibank Activate Restriction

A subsequent ACTIVATE command to a different row in the same bank can only be issued after the previous active row has been closed (precharged).

같은 bank 내의 다른 행에 대한 이후의 ACTIVATE 명령은 이전에 활성화되었던 행이 닫히고 (precharge가 된 후)에만 내릴 수 있습니다.

The minimum time interval between successive ACTIVATE commands to the same bank is defined by tRC.

같은 bank에 연속적으로 주어진 ACTIVATE 명령 사이의 최소 시간 간격은 tRC에 의해 정의됩니다.

A subsequent ACTIVATE command to another bank can be issued while the first bank is being accessed, which results in a reduction of total row-access overhead.

다른 bank에 대한 이후의 ACTIVATE 명령은 첫 번째 bank가 접근 중일 때 내릴 수 있으며, 이로 인해 총 row-access 오버헤드가 감소하게 됩니다.

※오버헤드(overhead) : 어떤 처리를 하기 위해 들어가는 간접적인 처리 시간 · 메모리 등을 말한다.

예를 들어 A라는 처리를 단순하게 실행한다면 10초 걸리는데, 안전성을 고려하고 부가적인 B라는 처리를 추가한 결과 처리시간이 15초 걸렸다면, 오버헤드는 5초가 된다. 또한 이 처리 B를 개선해 B'라는 처리를 한 결과, 처리시간이 12초가 되었다면, 이 경우 오버헤드가 3초 단축되었다고 말한다.

DDR2 devices with 8 banks (1Gb or larger) have an additional requirement: tFAW.

8개의 bank를 가진 DDR2 장치들 (1Gb 또는 그 이상의 크기)은 추가적인 요구 사항인 tFAW를 가지고 있습니다.

This requires no more than four ACTIVATE commands may be issued in any given tFAW(MIN) period, as shown in Figure 45.

이는 주어진 tFAW(MIN) 기간 동안 네 개 이상의 ACTIVATE 명령을 내릴 수 없음을 요구하며, 이 내용은 Figure 45에서 보여집니다.

특정 bank의 행을 open하는데 사용

Bank Address 값에 따라 Bank가 결정되고 Address값에 따라 행이 선택

open한 행은 bank에 Precharge command가 실행되기 될 때 까지 open으로 유지

같은 bank에서 다른 행을 열기 전에 Precharge command를 실행

Activate

Meeting tRRD (MIN) and tRCD (MIN)

Before any READ or WRITE commands can be issued to a bank within the DDR2 SDRAM, a row in that bank must be opened (activated), even when additive latency is used.

DDR2 SDRAM 내의 bank에 어떤 읽기(READ) 혹은 쓰기(WRITE) 명령을 내리기 전에는, 해당 bank의 행(row)이 열려있어야 합니다. 이는 additive latency(AL)가 사용되는 경우에도 마찬가지입니다.

This is accomplished via the ACTIVATE command, which selects both the bank and the row to be activated.

이것은 ACTIVATE 명령을 통해 이루어지며, 이 명령은 활성화될 bank와 행(row)을 모두 선택합니다.

After a row is opened with an ACTIVATE command, a READ or WRITE command may be issued to that row subject to the tRCD specification.

ACTIVATE 명령을 사용해 행(row)이 열린 후에는, 해당 행에 READ 또는 WRITE 명령을 내릴 수 있습니다. 이는 tRCD 사양에 따라 가능합니다.

tRCD (MIN) should be divided by the clock period and rounded up to the next whole number to determine the earliest clock edge after the ACTIVATE command on which a READ or WRITE command can be entered.

tRCD (MIN)은 클럭 주기로 나눈 후, 그 결과를 다음 정수로 올려야 합니다. 이는 ACTIVATE 명령 후에 가장 빠른 클럭 엣지를 결정하기 위함이며, 이 클럭 엣지에서 READ 또는 WRITE 명령이 입력될 수 있습니다.

The same procedure is used to convert other specification limits from time units to clock cycles.

시간 단위의 다른 사양 제한을 클럭 주기로 변환하기 위해 같은 절차가 사용됩니다.

For example, a tRCD (MIN) specification of 20ns with a 266 MHz clock (tCK = 3.75ns) results in 5.3 clocks, rounded up to 6.

예를 들어, 266 MHz 클럭 (tCK = 3.75ns)을 가지고 20ns의 tRCD (MIN) 사양이 있다면, 이는 5.3 clock으로 결과가 나오며, 이는 6으로 올림됩니다.

This is shown in Figure 44, which covers any case where 5 < tRCD (MIN)/tCK ≤ 6.

Figure 44에서 이 내용이 보여지며, 이 그림은 5 < tRCD (MIN)/tCK ≤ 6인 모든 경우를 포괄하고 있습니다.

Figure 44 also shows the case for tRRD where 2 < tRRD (MIN)/tCK ≤ 3."

Figure 44는 또한 tRRD (MIN)/tCK이 2보다 크고 3보다 작거나 같은 경우의 tRRD 사례를 보여줍니다.

Multibank Activate Restriction

A subsequent ACTIVATE command to a different row in the same bank can only be issued after the previous active row has been closed (precharged).

같은 bank 내의 다른 행에 대한 이후의 ACTIVATE 명령은 이전에 활성화되었던 행이 닫히고 (precharge가 된 후)에만 내릴 수 있습니다.

The minimum time interval between successive ACTIVATE commands to the same bank is defined by tRC.

같은 bank에 연속적으로 주어진 ACTIVATE 명령 사이의 최소 시간 간격은 tRC에 의해 정의됩니다.

A subsequent ACTIVATE command to another bank can be issued while the first bank is being accessed, which results in a reduction of total row-access overhead.

다른 bank에 대한 이후의 ACTIVATE 명령은 첫 번째 bank가 접근 중일 때 내릴 수 있으며, 이로 인해 총 row-access 오버헤드가 감소하게 됩니다.

※오버헤드(overhead) : 어떤 처리를 하기 위해 들어가는 간접적인 처리 시간 · 메모리 등을 말한다.

예를 들어 A라는 처리를 단순하게 실행한다면 10초 걸리는데, 안전성을 고려하고 부가적인 B라는 처리를 추가한 결과 처리시간이 15초 걸렸다면, 오버헤드는 5초가 된다. 또한 이 처리 B를 개선해 B'라는 처리를 한 결과, 처리시간이 12초가 되었다면, 이 경우 오버헤드가 3초 단축되었다고 말한다.

DDR2 devices with 8 banks (1Gb or larger) have an additional requirement: tFAW.

8개의 bank를 가진 DDR2 장치들 (1Gb 또는 그 이상의 크기)은 추가적인 요구 사항인 tFAW를 가지고 있습니다.

This requires no more than four ACTIVATE commands may be issued in any given tFAW(MIN) period, as shown in Figure 45.

이는 주어진 tFAW(MIN) 기간 동안 네 개 이상의 ACTIVATE 명령을 내릴 수 없음을 요구하며, 이 내용은 Figure 45에서 보여집니다.