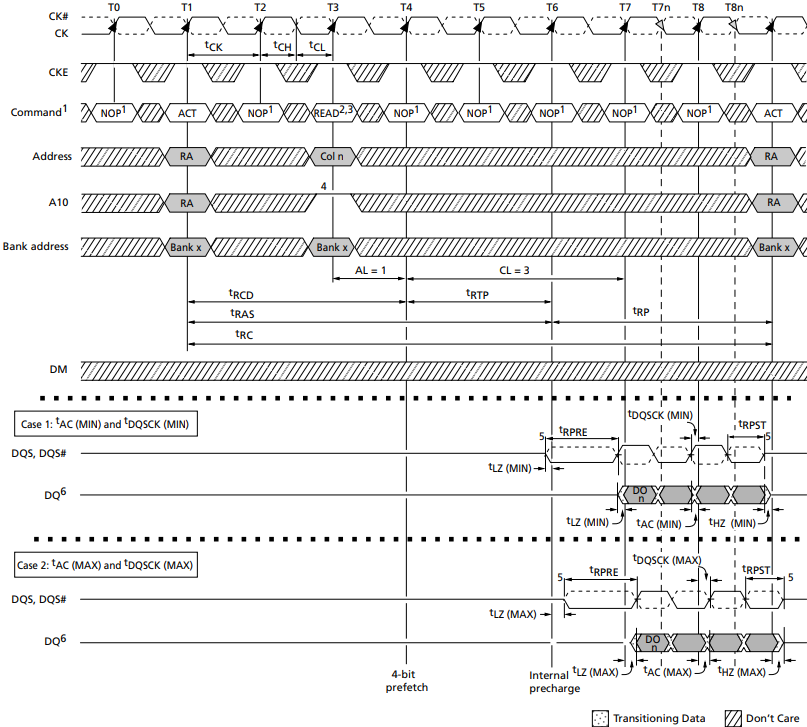

BA(bank address)값에 따라 bank가 결정되고, A0 ~ Axx(address)값에 따라 시작 열(Column)의 위치가 선택

A10은 read/write 후 precharge명령을 자동으로 실행할지 결정(auto precharge)

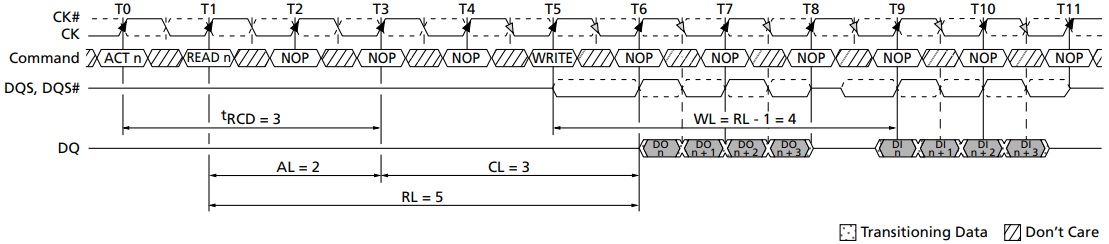

Activate 와 Read/Write사이에는 일정 시간(tRCD) 경과해야 한다. AL(Additive Latency)를 사용하여 Read/Write 실행을 AL clock 만큼 지연시켜 tRCD이 경과하기 전에 Read 또는 Write 명령을 내림

READ

READ bursts are initiated with a READ command. The starting column and bank addresses are provided with the READ command, and auto precharge is either enabled or disabled for that burst access. If auto precharge is enabled, the row being accessed is automatically precharged at the completion of the burst. If auto precharge is disabled, the row will be left open after the completion of the burst.

READ burst는 READ command으로 시작됩니다. 시작 열(column)과 bank address는 READ command과 함께 제공되며, burst 접근에 대해 auto precharge가 활성화되거나 비활성화됩니다. 자동 프리차지가 활성화되면, 접근 중인 행(row)은 burst 완료 후 자동으로 precharge됩니다. auto precharge가 비활성화되면, burst 완료 후에도 행(row)은 열린(open) 상태로 남습니다.

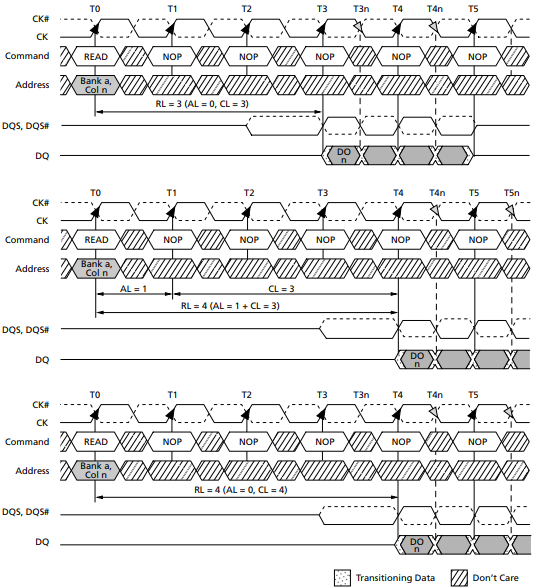

During READ bursts, the valid data-out element from the starting column address will be available READ latency (RL) clocks later. RL is defined as the sum of AL and CL: RL = AL + CL. The value for AL and CL are programmable via the MR and EMR commands, respectively. Each subsequent data-out element will be valid nominally at the next positive or negative clock edge (at the next crossing of CK and CK#). Figure 46 shows examples of RL based on different AL and CL settings.

READ burst 동안에는 시작 열(row) 주소에서 유효한 데이터 출력 요소가 READ latency (RL) 클럭 후에 사용 가능합니다. RL은 AL과 CL의 합으로 정의됩니다: RL = AL + CL. AL과 CL의 값은 각각 MR 및 EMR command을 통해 프로그래밍할 수 있습니다. 각 후속 데이터 출력 요소는 명목상 다음 positive 또는 negative 클럭 엣지에서 유효하게 됩니다 (CK와 CK#의 다음 교차점에서). Figure 46은 다양한 AL과 CL 설정에 기반한 RL의 예를 보여줍니다.

DQS/DQS# is driven by the DDR2 SDRAM along with output data. The initial LOW state on DQS and the HIGH state on DQS# are known as the read preamble (tRPRE). The LOW state on DQS and the HIGH state on DQS# coincident with the last data-out element are known as the read postamble (tRPST).

DQS/DQS#는 출력 데이터와 함께 DDR2 SDRAM에 의해 구동됩니다. DQS의 초기 LOW 상태와 DQS#의 HIGH 상태를 read preamble(tRPRE)라고 합니다. 마지막 데이터 출력 요소와 동시에 DQS의 LOW 상태와 DQS#의 HIGH 상태를 read postamble(tRPST)라고 합니다.

Upon completion of a burst, assuming no other commands have been initiated, the DQ will go High-Z. A detailed explanation of tDQSQ (valid data-out skew), tQH (data-out window hold), and the valid data window are depicted in Figure 55 and Figure 56. A detailed explanation of tDQSCK (DQS transition skew to CK) and tAC (data-out transition skew to CK) is shown in Figure 57.

burst가 완료되면 다른 명령이 시작되지 않은 경우 DQ는 High-Z 상태가 됩니다. tDQSQ (유효 데이터 출력 스큐), tQH (데이터 출력 윈도우 홀드), 그리고 유효 데이터 윈도우에 대한 상세 설명은 Figure 55와 Figure 56에 나타나 있습니다. tDQSCK (DQS 전환 스큐에서 CK까지) 및 tAC (데이터 출력 전환 스큐에서 CK까지)에 대한 자세한 설명은 Figure 57에 표시되어 있습니다.

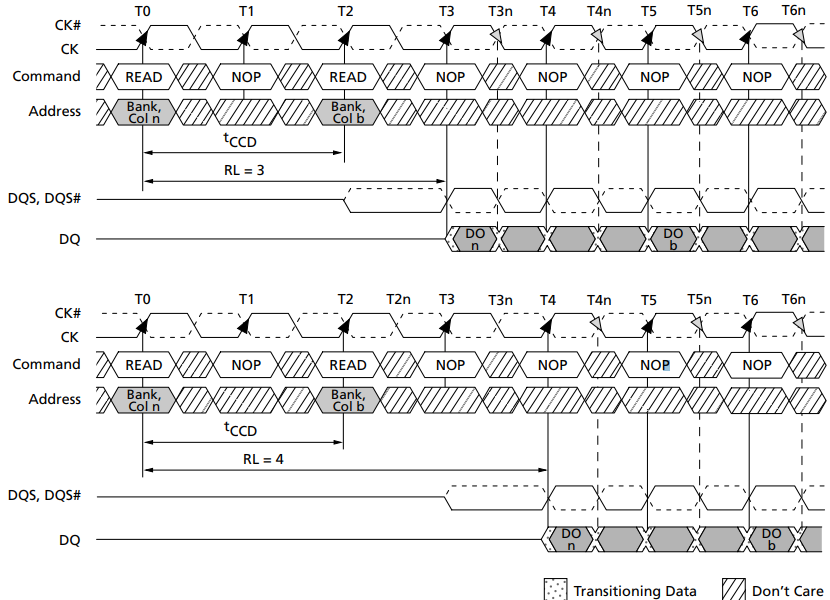

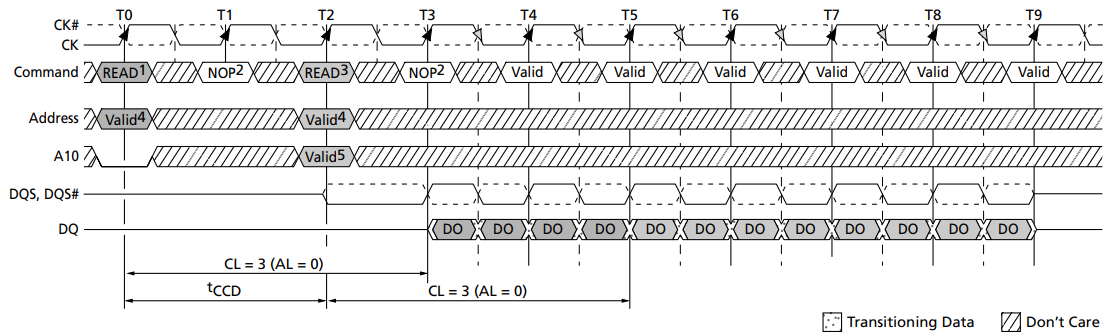

Data from any READ burst may be concatenated with data from a subsequent READ command to provide a continuous flow of data. The first data element from the new burst follows the last element of a completed burst. The new READ command should be issued x cycles after the first READ command, where x equals BL/2 cycles (see Figure 47).

어떤 READ burst에서의 데이터든지 이후의 READ 명령에서의 데이터와 연결될 수 있어, 연속적인 데이터 흐름을 제공할 수 있습니다. 새로운 버스트의 첫 번째 데이터 요소는 완료된 버스트의 마지막 요소를 따릅니다. 새로운 READ 명령은 첫 번째 READ 명령 후 x 사이클에 발행되어야 하는데, 여기서 x는 BL/2 사이클입니다(그림 47 참조).

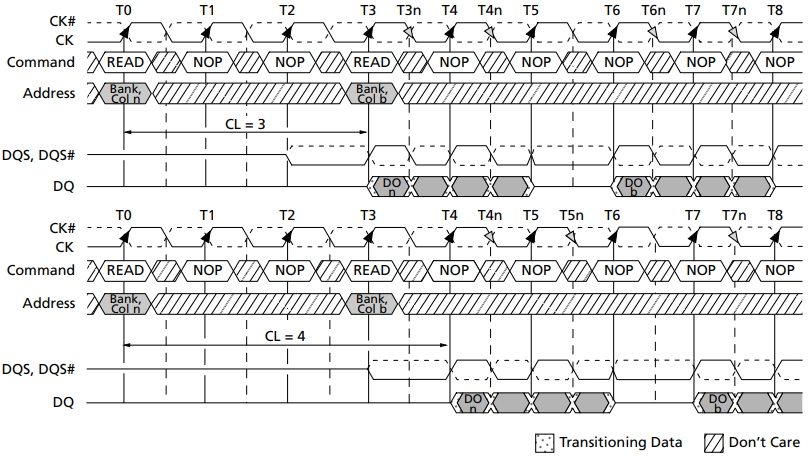

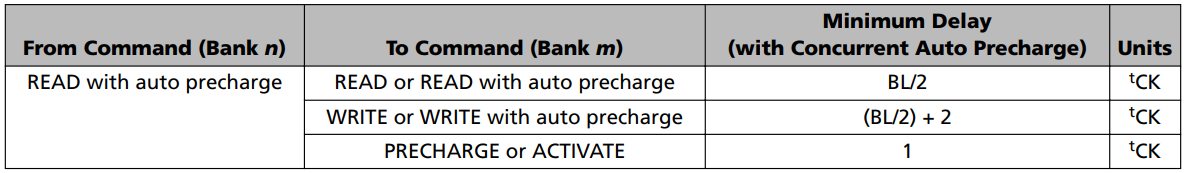

Nonconsecutive read data is illustrated in Figure 48. Full-speed random read accesses within a page (or pages) can be performed. DDR2 SDRAM supports the use of concurrent auto precharge timing (see Table 42).

비연속적(Nonconsecutive)인 READ 데이터는 Figure 48에서 보여집니다. 페이지(또는 페이지들) 내에서 Full-speed random read accesses이 수행될 수 있습니다. DDR2 SDRAM은 concurrent auto precharge timing의 사용을 지원합니다(Table 42 참조).

DDR2 SDRAM does not allow interrupting or truncating of any READ burst using BL = 4 operations. Once the BL = 4 READ command is registered, it must be allowed to complete the entire READ burst. However, a READ (with auto precharge disabled) using BL = 8 operation may be interrupted and truncated only by another READ burst as long as the interruption occurs on a 4-bit boundary due to the 4n prefetch architecture of DDR2 SDRAM. As shown in Figure 49, READ burst BL = 8 operations may not be interrupted or truncated with any other command except another READ command.

DDR2 SDRAM은 BL = 4 연산을 사용하는 어떤 READ burst도 중단하거나 줄이는 것을 허용하지 않습니다. 한번 BL = 4 READ 명령이 등록되면, 전체 READ 버스트를 완료해야 합니다. 그러나, BL = 8 연산을 사용하는 READ(auto precharge이 비활성화된 경우)는 다른 READ burst에 의해 중단되고 줄어들 수 있습니다. 이는 DDR2 SDRAM의 4n 프리페치 아키텍처 때문에 중단이 4비트 경계에서 발생하기 때문입니다. Figure 49에서 보여지는 것처럼, READ burst BL = 8 연산은 다른 READ 명령 외에는 어떤 다른 명령으로도 중단되거나 줄어들지 않습니다.

Data from any READ burst must be completed before a subsequent WRITE burst is allowed. An example of a READ burst followed by a WRITE burst is shown in Figure 50. The tDQSS (NOM) case is shown (tDQSS [MIN] and tDQSS [MAX] are defined in Figure 58).

어떤 READ burst의 데이터도 후속 WRITE burst가 허용되기 전에 완료되어야 합니다. READ burst 뒤에 이어지는 WRITE burst의 예는 Figure 50에서 확인할 수 있습니다. tDQSS (NOM) 경우가 보여집니다 (tDQSS [MIN]과 tDQSS [MAX]는 Figure 58에서 정의됩니다).

READ with Precharge

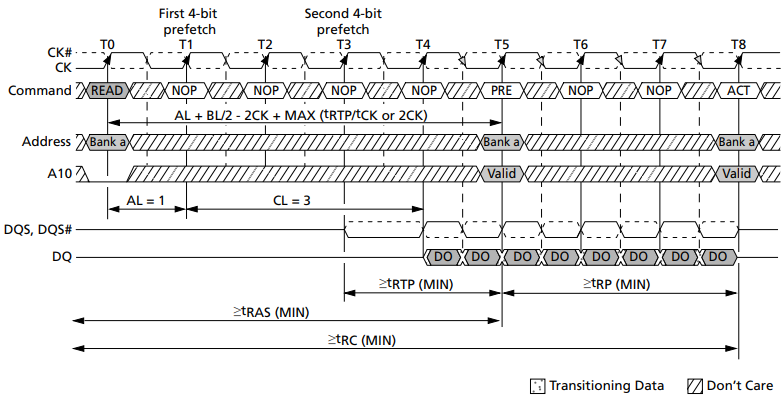

A READ burst may be followed by a PRECHARGE command to the same bank, provided auto precharge is not activated. The minimum READ-to-PRECHARGE command spacing to the same bank has two requirements that must be satisfied: AL + BL/2 clocks and tRTP. tRTP is the minimum time from the rising clock edge that initiates the last 4-bit prefetch of a READ command to the PRECHARGE command. For BL = 4, this is the time from the actual READ (AL after the READ command) to PRECHARGE command. For BL = 8, this is the time from AL + 2 × CK after the READ-to-PRECHARGE command. Following the PRECHARGE command, a subsequent command to the same bank cannot be issued until tRP is met. However, part of the row precharge time is hidden during the access of the last data elements.

READ burst는 AUTO PRECHARGE가 활성화되지 않은 경우 동일한 bank에 대한 PRECHARGE 명령어로 이어질 수 있습니다. 동일한 bank에 대한 READ-to-PRECHARGE 명령 간격의 최소값은 AL + BL/2 클럭과 tRTP 두 가지 요구사항을 모두 충족해야 합니다. tRTP는 READ 명령의 마지막 4비트 프리페치를 시작하는 상승 클럭 에지부터 PRECHARGE 명령까지의 최소 시간입니다. BL = 4의 경우, 이는 실제 READ (READ 명령 이후의 AL)에서 PRECHARGE 명령까지의 시간입니다. BL = 8인 경우, 이는 READ-to-PRECHARGE 명령 후의 AL + 2 × CK 시간입니다. PRECHARGE 명령 다음에 동일한 bank에 대한 후속 명령은 tRP를 충족할 때까지 발행될 수 없습니다. 그러나 행 PRECHARGE 시간의 일부는 마지막 데이터 요소에 접근하는 동안 숨겨집니다.

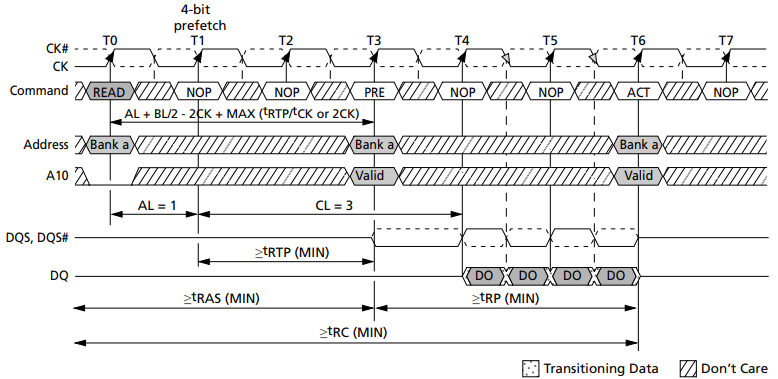

Examples of READ-to-PRECHARGE for BL = 4 are shown in Figure 51 and in Figure 52 for BL = 8. The delay from READ-to-PRECHARGE period to the same bank is AL + BL/2 - 2CK + MAX (tRTP/tCK or 2 × CK) where MAX means the larger of the two.

BL = 4에 대한 READ-to-PRECHARGE의 예는 Figure 51에, BL = 8에 대한 예는 Figure 52에 나와 있습니다. 동일한 bank에 대한 READ-to-PRECHARGE 의 delay는 AL + BL/2 - 2CK + MAX (tRTP/tCK 또는 2 × CK)이며, 여기서 MAX는 두 값 중 큰 값을 의미합니다.

READ with Auto Precharge

If A10 is high when a READ command is issued, the READ with auto precharge function is engaged. The DDR2 SDRAM starts an auto precharge operation on the rising clock edge that is AL + (BL/2) cycles later than the read with auto precharge command provided tRAS (MIN) and tRTP are satisfied. If tRAS (MIN) is not satisfied at this rising clock edge, the start point of the auto precharge operation will be delayed until tRAS (MIN) is satisfied. If tRTP (MIN) is not satisfied at this rising clock edge, the start point of the auto precharge operation will be delayed until tRTP (MIN) is satisfied. When the internal precharge is pushed out by tRTP, tRP starts at the point where the internal precharge happens (not at the next rising clock edge after this event).

READ 명령이 발행될 때 A10이 높으면, auto precharge와 함께 READ가 활성화됩니다. DDR2 SDRAM은 tRAS (MIN)과 tRTP가 충족되는 한, auto precharge보다 AL + (BL/2) 사이클 뒤의 rising 에지에서 auto precharge을 시작합니다. 만약 이 rising 에지에서 tRAS (MIN)이 충족되지 않으면, auto precharge의 시작점이 tRAS (MIN)이 충족될 때까지 지연됩니다. 만약 이 rising 에지에서 tRTP (MIN)이 충족되지 않으면, auto precharge의 시작점이 tRTP (MIN)이 충족될 때까지 지연됩니다. internal precharge이 tRTP에 의해 밀릴 때, tRP는 internal precharge이 발생하는 지점에서 시작합니다 (이 사건 후의 다음 rising edge가 아닙니다).

When BL = 4, the minimum time from READ with auto precharge to the next ACTIVATE command is AL + (tRTP + tRP)/tCK. When BL = 8, the minimum time from READ with auto precharge to the next ACTIVATE command is AL + 2 clocks + (tRTP + tRP)/tCK. The term (tRTP + tRP)/tCK is always rounded up to the next integer. A general purpose equation can also be used: AL + BL/2 - 2CK + (tRTP + tRP)/tCK. In any event, the internal precharge does not start earlier than two clocks after the last 4-bit prefetch.

BL = 4일 때, auto precharge과 함께 READ부터 다음 ACTIVATE 명령까지의 최소 시간은 AL + (tRTP + tRP)/tCK입니다. BL = 8일 때, auto precharge과 함께 READ부터 다음 ACTIVATE 명령까지의 최소 시간은 AL + 2 Clock + (tRTP + tRP)/tCK입니다. (tRTP + tRP)/tCK 항은 항상 다음 정수로 반올림됩니다. 일반적인 목적의 방정식도 사용될 수 있습니다: AL + BL/2 - 2CK + (tRTP + tRP)/tCK. 어떠한 경우에도, internal precharge은 마지막 4비트 프리페치 후 최소 2 Clock이 지나야 시작됩니다.

READ with auto precharge command may be applied to one bank while another bank is operational. This is referred to as concurrent auto precharge operation, as noted in Table 42. Examples of READ with precharge and READ with auto precharge with applicable timing requirements are shown in Figure 53 and Figure 54, respectively

auto precharge 기능이 있는 READ 명령은 다른 bank가 작동 중인 상태에서 한 bank에 적용될 수 있습니다. 이를 'concurrent auto precharge operation'이라고 하며, 이는 Table 42에서 언급되었습니다. precharge와 READ 기능이 있는 auto precharge의 예시와 적용 가능한 타이밍 요구사항은 각각 Figure 53과 Figure 54에서 보여줍니다.