반응형

4bit_가감산기

Design Source

`timescale 1ns / 1ps

module FullAddersub_4bit(

input [3:0] i_a, i_b,

input i_mode,

output [3:0] o_sum,

output o_carry

);

wire [3:0] w_b;

assign w_b = {4{i_mode}} ^ i_b; // 4는 반복 수

FullAdder_4bit AdderSub(

.i_a(i_a),

.i_b(w_b),

.i_carry_in(i_mode),

.o_sum(o_sum),

.o_carry(o_carry)

);

endmodule

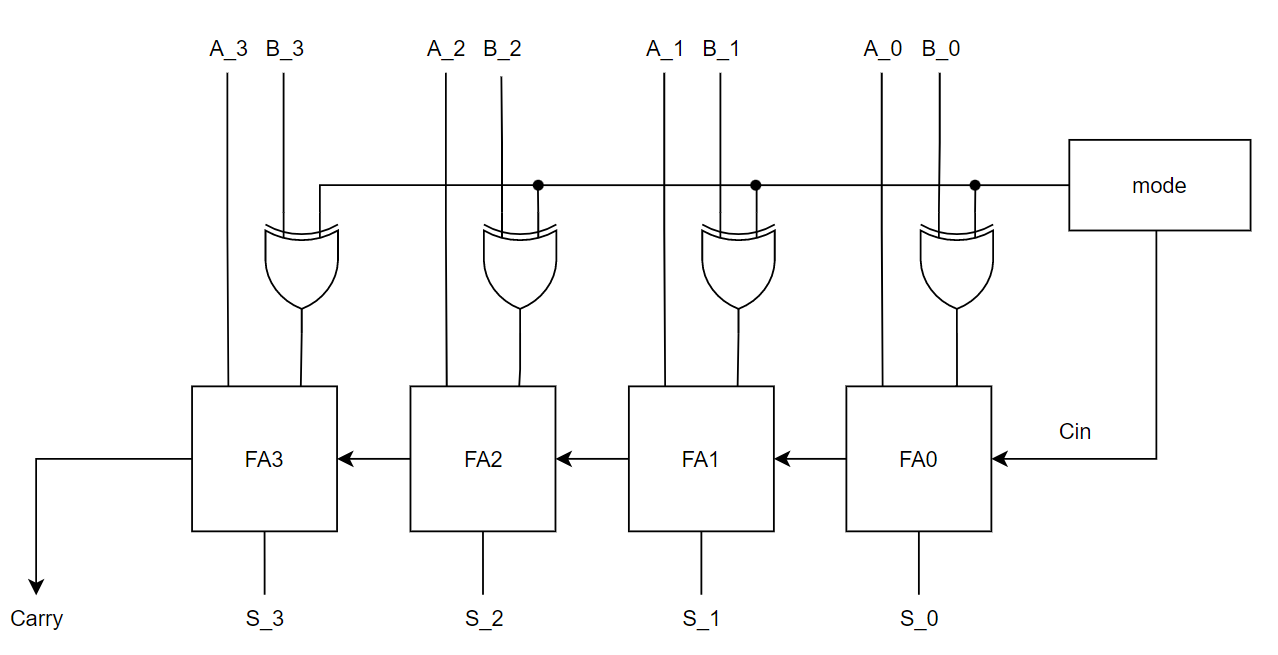

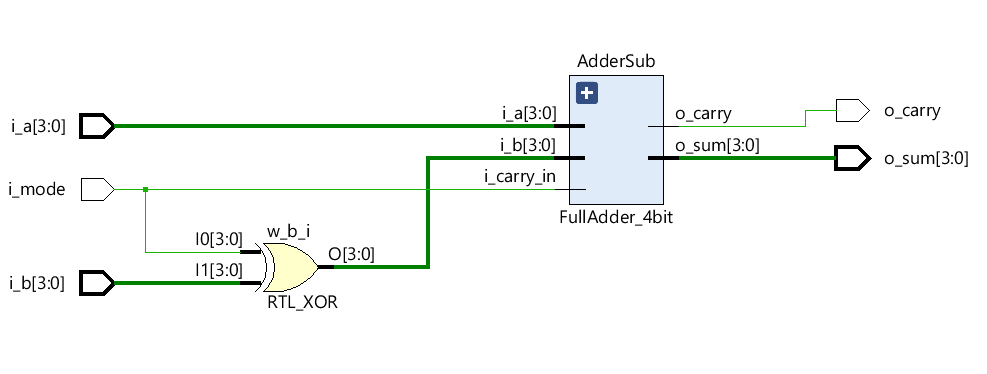

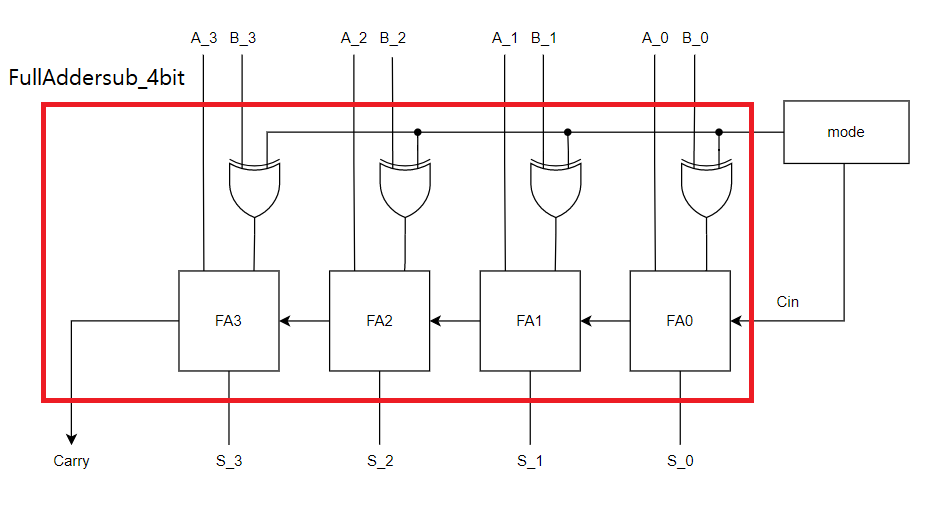

Schematic

Simulation Source

`timescale 1ns / 1ps

module tb_FullAddersub_4bit();

reg [3:0] i_a, i_b;

reg i_mode;

wire [3:0] o_sum;

wire o_carry;

FullAddersub_4bit dut(

.i_a(i_a),

.i_b(i_b),

.i_mode(i_mode), // 1bit

.o_sum(o_sum),

.o_carry(o_carry)

);

initial begin

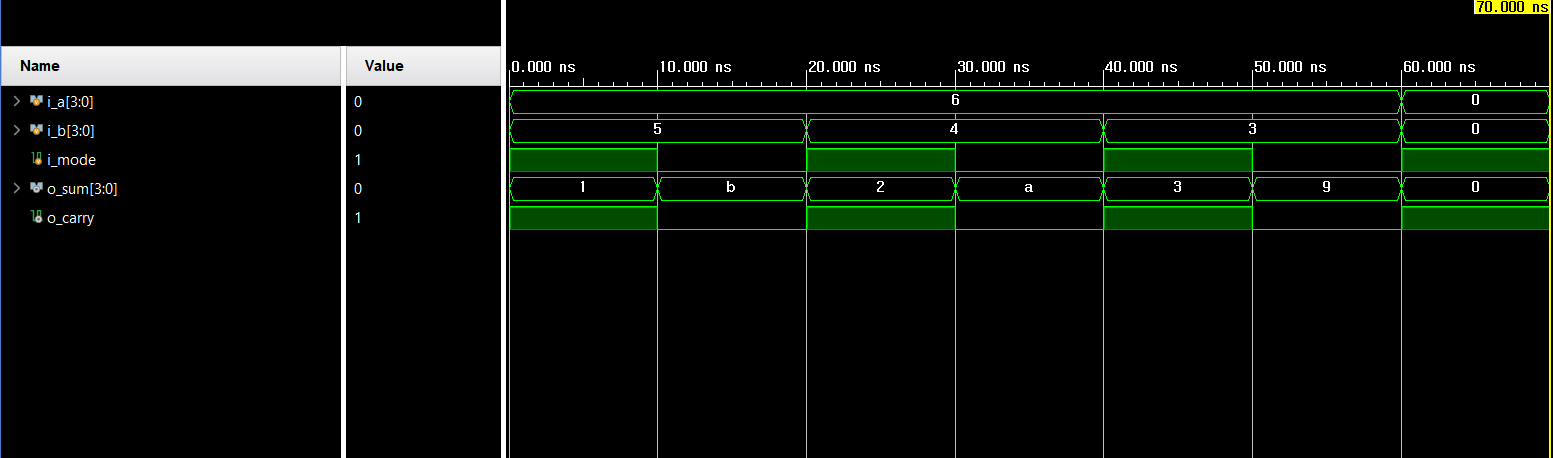

#00 i_a = 4'd6; i_b = 4'd5; i_mode = 4'd1;

#10 i_a = 4'd6; i_b = 4'd5; i_mode = 4'd0;

#10 i_a = 4'd6; i_b = 4'd4; i_mode = 4'd1;

#10 i_a = 4'd6; i_b = 4'd4; i_mode = 4'd0;

#10 i_a = 4'd6; i_b = 4'd3; i_mode = 4'd1;

#10 i_a = 4'd6; i_b = 4'd3; i_mode = 4'd0;

#10 i_a = 4'd0; i_b = 4'd0; i_mode = 4'd1;

#10 $finish;

end

endmodule

Timing Chart

constraints

## Switches

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports { i_a[0] }]; #IO_L19N_T3_A09_D25_VREF_14 ,Sch=SW0

set_property -dict { PACKAGE_PIN V16 IOSTANDARD LVCMOS33 } [get_ports { i_a[1] }]; #IO_L19P_T3_A10_D26_14 ,Sch=SW1

set_property -dict { PACKAGE_PIN W16 IOSTANDARD LVCMOS33 } [get_ports { i_a[2] }]; #IO_L20P_T3_A08_D24_14 ,Sch=SW2

set_property -dict { PACKAGE_PIN W17 IOSTANDARD LVCMOS33 } [get_ports { i_a[3] }]; #IO_L20N_T3_A07_D23_14 ,Sch=SW3

set_property -dict { PACKAGE_PIN W15 IOSTANDARD LVCMOS33 } [get_ports { i_b[0] }]; #IO_L21N_T3_DQS_A06_D22_14 ,Sch=SW4

set_property -dict { PACKAGE_PIN V15 IOSTANDARD LVCMOS33 } [get_ports { i_b[1] }]; #IO_L21P_T3_DQS_14 ,Sch=SW5

set_property -dict { PACKAGE_PIN W14 IOSTANDARD LVCMOS33 } [get_ports { i_b[2] }]; #IO_L22N_T3_A04_D20_14 ,Sch=SW6

set_property -dict { PACKAGE_PIN W13 IOSTANDARD LVCMOS33 } [get_ports { i_b[3] }]; #IO_L22P_T3_A05_D21_14 ,Sch=SW7

set_property -dict { PACKAGE_PIN R2 IOSTANDARD LVCMOS33 } [get_ports { i_mode }]; #IO_L1P_T0_34 ,Sch=SW15

## LEDs

set_property -dict { PACKAGE_PIN U16 IOSTANDARD LVCMOS33 } [get_ports { o_sum[0]}]; #IO_L23N_T3_A02_D18_14 ,Sch=LED0

set_property -dict { PACKAGE_PIN E19 IOSTANDARD LVCMOS33 } [get_ports { o_sum[1]}]; #IO_L3N_T0_DQS_EMCCLK_14 ,Sch=LED1

set_property -dict { PACKAGE_PIN U19 IOSTANDARD LVCMOS33 } [get_ports { o_sum[2]}]; #IO_L15P_T2_DQS_RDWR_B_14 ,Sch=LED2

set_property -dict { PACKAGE_PIN V19 IOSTANDARD LVCMOS33 } [get_ports { o_sum[3]}]; #IO_L15N_T2_DQS_DOUT_CSO_B_14 ,Sch=LED3

set_property -dict { PACKAGE_PIN W18 IOSTANDARD LVCMOS33 } [get_ports { o_carry }]; #IO_L16P_T2_CSI_B_14 ,Sch=LED4

## Configuration options, can be used for all designs

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]4bit_전가산기 FPGA 회로 구성

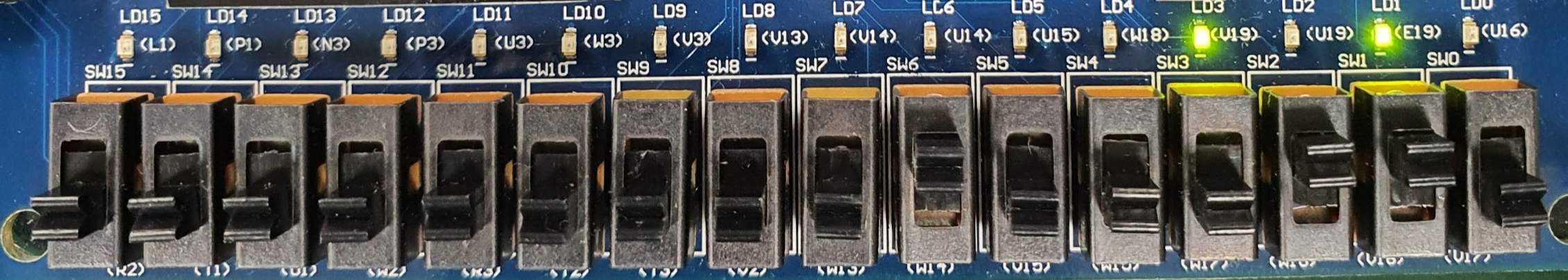

작동사진

| 입력 | 출력 | |||

| mode | B[4:0] | A[3:0] | sum[3:0] | carry |

| 0[+] | 0100[4] | 0110 [6] | 1010[10] | 0 |

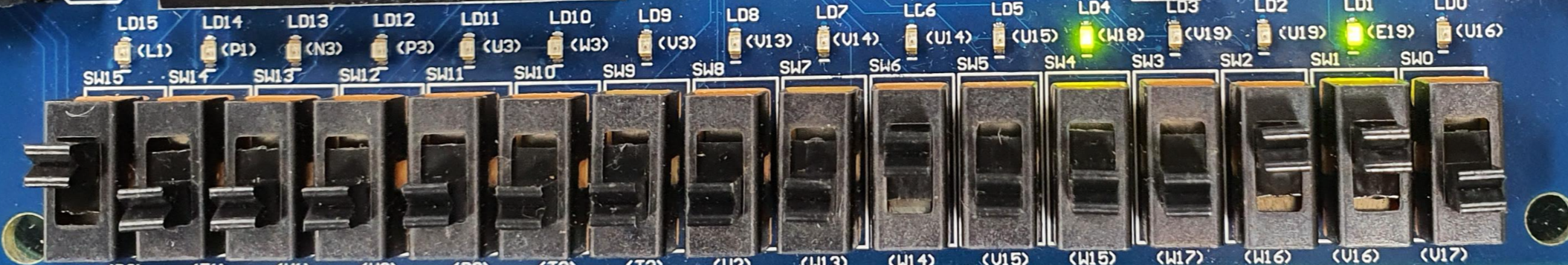

| 입력 | 출력 | |||

| mode | B[4:0] | A[3:0] | sum[3:0] | carry |

| 1[-] | 0100[4] | 0110 [6] | 0010[2] | 1 |

| 입력 | 출력 | |||

| mode | B[4:0] | A[3:0] | sum[3:0] | carry |

| 0[+] | 0101[5] | 0110 [6] | 1011[11] | 0 |

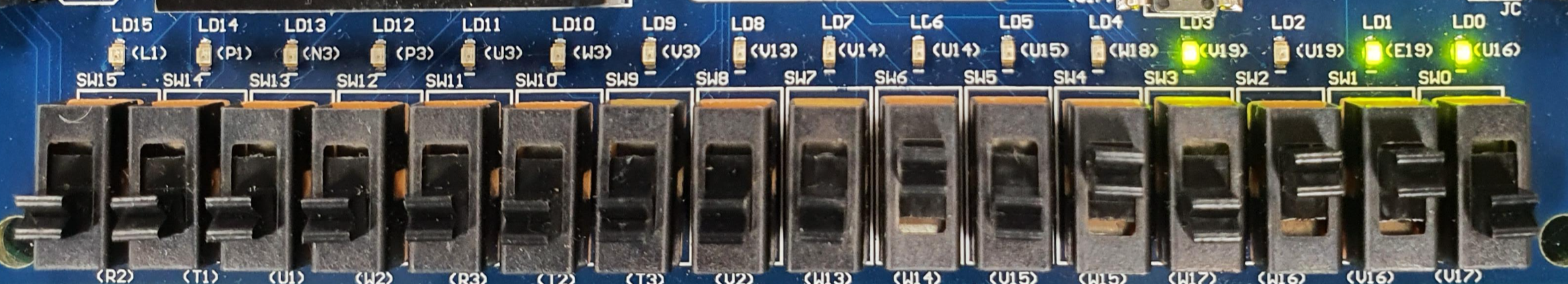

| 입력 | 출력 | |||

| mode | B[4:0] | A[3:0] | sum[3:0] | carry |

| 1[-] | 0101[5] | 0110 [6] | 0001[1] | 1 |

| 입력 | 출력 | |||

| mode | B[4:0] | A[3:0] | sum[3:0] | carry |

| 0[+] | 0011[3] | 0110[6] | 1001[9] | 0 |

| 입력 | 출력 | |||

| mode | B[4:0] | A[3:0] | sum[3:0] | carry |

| 1[-] | 0011[3] | 0110[6] | 0011[3] | 1 |

반응형